US007716267B2

## (12) United States Patent Ito et al.

(54) DECIMAL COMPUTING APPARATUS, ELECTRONIC DEVICE CONNECTABLE DECIMAL COMPUTING APPARATUS, ARITHMETIC OPERATION APPARATUS, ARITHMETIC OPERATION CONTROL APPARATUS, AND PROGRAM-RECORDED RECORDING MEDIUM

(75) Inventors: Hisashi Ito, Ome (JP); Tetsuichi Nakae,

Ome (JP)

(73) Assignee: Casio Computer Co., Ltd., Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 1184 days.

(21) Appl. No.: 11/109,888

(22) Filed: Apr. 19, 2005

(65) **Prior Publication Data**

US 2006/0047740 A1 Mar. 2, 2006

(30) Foreign Application Priority Data

Aug. 30, 2004

(JP)

2004-250678

Sep. 3, 2004

(JP)

2004-257057

(51) Int. Cl. G06F 7/38 G06F 7/50

(2006.01) (2006.01)

- (52) **U.S. Cl.** ...... 708/513; 708/680

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,021,655 A | *   | 5/1977 | Healey et al   | 708/518 |

|-------------|-----|--------|----------------|---------|

| 4.456.955 A | »jc | 6/1984 | Yanagita et al | 712/300 |

(10) Patent No.: US 7,716,267 B2 (45) Date of Patent: May 11, 2010

4,536,854 A \* 8/1985 Yanagita ...... 708/518

(Continued)

#### FOREIGN PATENT DOCUMENTS

JP 62-075838 A 4/1987

(Continued)

#### OTHER PUBLICATIONS

Suzuki, Hiroshi, "Accuracy Estimation Algorithm in Floating-Point Arithmetic Operation and its Evaluation." Research Report of Information Processing Society. Information Processing Society of Japan. Oct. 27, 1994: vol. 94, No. 92: pp. 27 to 33.

(Continued)

Primary Examiner—Chuong D Ngo (74) Attorney, Agent, or Firm—Frishauf, Holtz, Gooodman & Chick, P.C.

#### (57) ABSTRACT

Decimal calculation apparatus, which performs multidigit decimal calculation with the number of calculation digits set in calculation instruction, comprises multidigit memory section capable of storing values with greater numbers of digits than the number of digits of a predetermined digit unit in plurality of memory areas; calculation-instruction memory section which stores calculation instruction having the number of calculation digits and type of calculation set therein; and decimal calculation section which performs decimal calculation of sequentially calculating numerical values of corresponding digit units respectively stored in plurality of memory areas of the multidigit memory section, digit unit by digit unit in the number of calculation digits set in calculation instruction stored in calculation-instruction memory section, in decimal calculation according to type of calculation set in calculation instruction stored in calculation-instruction memory section, and sequentially writing calculation results in plurality of memory areas of multidigit memory section digit unit by digit unit.

#### 2 Claims, 39 Drawing Sheets

#### US 7,716,267 B2

Page 2

| U.S. PATENT DOCUMENTS | JP | 8-263264 A  | 10/1996 |

|-----------------------|----|-------------|---------|

|                       | JP | 09-190335 A | 7/1997  |

#### FOREIGN PATENT DOCUMENTS

| JР | 4-7737 A    | 1/1992  |

|----|-------------|---------|

| JP | 4-116717 A  | 4/1992  |

| JP | 05-089041 A | 4/1993  |

| JP | 5-233853 A  | 9/1993  |

| JP | 6-230964 A  | 8/1994  |

| JP | 7-287649 A  | 10/1995 |

#### OTHER PUBLICATIONS

Suda, Reiji. "2.1. The Comparison and the Conditional Branching." Basic C Language and Algorithm. Aug. 30, 2002. searched: Jun. 9, 2008. <a href="http://wwb.archive.org/web/20020830213509/http://www.na.cse.nagoya-u.ac.jp/-reiji/lect/alg01/sec2-1R.html">http://wwb.archive.org/web/20020830213509/http://www.na.cse.nagoya-u.ac.jp/-reiji/lect/alg01/sec2-1R.html</a>. Japanese Office Action dated Oct. 27, 2009 and English translation thereof issued in counterpart Japanese Application No. 2004-257057.

<sup>\*</sup> cited by examiner

FIG.

### FIG. 2A

FIG. 2B

COMPUTING Suad Sout -Fuad Fout → REGISTER SECTION 260 ᇤ Slad Flad **→** CONTROL SIGNAL ,233 ~~250 SELECTOR SELECTOR 254 216 MATCH CIRCUIT INSTRUCTION DECODER ADDRESS 232 VARIABLE PARAMETER MEMORY SECTION 240~ SELECTOR INSTRUCTION END SIGNAL 231 SELECTOR REGISTERS W LATCH SECTION 교 Sn Р 正 ೲ 22 10, 2 20, PROGRAM INSTRUCTION PROGRAM ROM PROGRAM COUNTER

Sout [15:0]Fout [15:0] EXPONENT PORTION 260 Fin [15 : 0] 4 Ŋ 9 REGISTER SECTION IMAGINARY PORTION ∞ Slad [3 : 0] တ LOWER ADDRESS 9 7 4 5 Flad [3 : 0] 4 WORD 15 Fuad [1:0] REGISTERS X Suad [1:0]

# FIG. 5

| Fuad , Suad | REGISTERS |

|-------------|-----------|

| 00          | X         |

| 01          | Y         |

| 10          | Z         |

| 11          | A         |

FIG. 7

US 7,716,267 B2

|          |           | EXT                                                        |                                      |                      | FUNC               | NOIT           | FUNCTION EXAMPLES          |                                                                  |

|----------|-----------|------------------------------------------------------------|--------------------------------------|----------------------|--------------------|----------------|----------------------------|------------------------------------------------------------------|

| PATTERNS |           | SERIAL/                                                    | DIRECT/                              | INSTRUCTION          | ICTION             |                |                            |                                                                  |

|          | VALUE     | 1-WORD<br>INSTRUCTION                                      | INDIRECT<br>ADDRESSING               | IMAGINARY<br>PORTION | OPERAND<br>PORTION |                | MNEMONIC                   | OPERATION                                                        |

| (A)      | 000       | SERIAL WORD                                                | DIRECT<br>ADDRESSING                 | ADD 000              | X15 Y4             | γ4             | X4~15+Y                    | X4~15+Y4~15→X4~15                                                |

| (B)      | 010       | SERIAL WORD                                                | INDIRECT<br>ADDRESSING               | ADD 010              | X15                | **             | Xv~15+Y                    | Xv~15+Yv~15→Xv~15                                                |

| (C)      | 100       | SERIAL WORD                                                | INDIRECT<br>ADDRESSING               | ADD 100              | *X                 | Y4             | X4 ~ w+Y                   | $X4 \sim w + Y4 \sim w \rightarrow X4 \sim w$                    |

| (D)      | 110       | SERIAL WORD                                                | INDIRECT<br>ADDRESSING               | ADD 110              | **                 | <b>*</b>       | Xv~w+Y                     | Xv~w+Yv~w→Xv~w                                                   |

| (E)      | 100       | 1-WORD                                                     | DIRECT<br>ADDRESSING                 | ADD 001              | X15 Y4             | γ4             | X15+Y4                     | X15+Y4 → X15                                                     |

| (F)      | 011       | 1-WORD                                                     | INDIRECT<br>  ADDRESSING             | ADD 011              | X15                | Υ*             | X15+Yv                     | X15+Yv → X15                                                     |

| (5)      | 101       | 1-WORD                                                     | INDIRECT<br>ADDRESSING               | ADD 101              | *×                 | Y4             | Xw+Y4                      | Xw+Y4→Xw                                                         |

| (H)      | 111       | 1-WORD                                                     | INDIRECT<br>ADDRESSING               | ADD 111              | *×                 | *\             | Xw+Yv                      | Xw+Yv → Xw                                                       |

|          | . σ.π. *. | ADD: ADDITION<br>Rn: VALUE STORED IN<br>*: ARBITRARY VALUE | ED IN n-TH WORD IN REGISTER R<br>LUE | IN REGISTER          | R                  | w: D/<br>v: DA | ATA w STORE<br>TA v STOREI | w: DATA w STORED IN REGISTER W<br>v: DATA v STORED IN REGISTER V |

FIG. 10

FIG. 11

|                |                                                  | EXT                                                               |                                                                                                  |                      | FUNCI              | FUNCTION EXAMPLES                                 |                                                                                                    |

|----------------|--------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------|--------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------|

| PATTERNS       |                                                  | SERIAL                                                            | DIRECT/                                                                                          | INSTRUCTION          | ICTION             |                                                   |                                                                                                    |

|                | VALUE                                            | 1-WORD<br>INSTRUCTION                                             | INDIRECT<br>ADDRESSING                                                                           | IMAGINARY<br>PORTION | OPERAND<br>PORTION | D MNEMONIC                                        | OPERATION                                                                                          |

| (1)            | 0000                                             | SERIAL WORD                                                       | DIRECT<br>ADDRESSING                                                                             | ADD 0000             | X15 Y4             | 4 X4~15+Y                                         | X4~15+Y4~15→X4~15                                                                                  |

| (r)            | 0010                                             | SERIAL WORD                                                       | INDIRECT<br>ADDRESSING                                                                           | ADD 0010             | X15 Y*             | * Xv~15+Y                                         | Xv ~15+Yv ~15 → Xv ~15                                                                             |

| (K)            | 0100                                             | SERIAL WORD                                                       | INDIRECT<br>ADDRESSING                                                                           | ADD 0100             | X15 Y*             | * Xi~15+Y                                         | Xi ~15+Yi ~15 →Xi ~15                                                                              |

| (T)            | 1000                                             | SERIAL WORD                                                       | INDIRECT<br>ADDRESSING                                                                           | ADD 1000             | X* Y4              | 4 X4 ~ w+Y                                        | X4 ~w+Y4 ~w→X4~w                                                                                   |

| (M)            | 1010                                             | SERIAL WORD                                                       | INDIRECT<br>ADDRESSING                                                                           | ADD 1010             | *Y *X              | λ+м~∧X *                                          | Xv~w+Yv~w→Xv~w                                                                                     |

| (N)            | 1100                                             | SERIAL WORD                                                       | INDIRECT<br>ADDRESSING                                                                           | ADD 1100             | *Y *X              | * Xi~w+Y                                          | Xi~w+Yi~w→Xi~w                                                                                     |

| (0)            | 0001                                             | 1-WORD                                                            | DIRECT<br>ADDRESSING                                                                             | ADD 0001             | X15 Y4             | 4 X15+Y4                                          | X15+Y4 → X15                                                                                       |

| (P)            | 0011                                             | 1-WORD                                                            | INDIRECT<br>ADDRESSING                                                                           | ADD 0011             | X15 Y*             | * X15+Yv                                          | X15+Yv → X15                                                                                       |

| (O)            | 0101                                             | 1-WORD                                                            | INDIRECT<br>ADDRESSING                                                                           | ADD 0101             | X15 Y*             | * X15+Yi                                          | X15+Y i → X15                                                                                      |

| (R)            | 1001                                             | 1-WORD                                                            | INDIRECT<br>ADDRESSING                                                                           | ADD 1001             | X* Y4              | 4 Xw+Y4                                           | Xw+Y4→Xw                                                                                           |

| (S)            | 1011                                             | 1-WORD                                                            | INDIRECT<br>ADDRESSING                                                                           | ADD 1011             | ×* γ*              | * Xw+Yv                                           | Xw+Yv → Xw                                                                                         |

| (T)            | 1101                                             | 1-WORD                                                            | INDIRECT<br>ADDRESSING                                                                           | ADD 1101             | ** Y*              | * Xw+Yi                                           | Xw+Yi → Xw                                                                                         |

| ADD:<br>Rn: V. | ADD: ADDITION<br>Rn: VALUE STO<br>*: ARBITRARY V | ADD: ADDITION<br>Rn: VALUE STORED IN n-TH W<br>*: ARBITRARY VALUE | ADD: ADDITION<br>Rn: VALUE STORED IN n-TH WORD OR n-TH DIGIT IN REGISTER R<br>↑: ARBITRARY VALUE | SIT IN REGIST        |                    | v: DATA w STOF<br>r: DATA v STORI<br>DATA i STORE | w: DATA w STORED IN REGISTER W<br>v: DATA v STORED IN REGISTER V<br>i: DATA i STORED IN REGISTER I |

FIG. 13

|                                                                                                                     |                                                                                                                                                                                                                               | $\overline{}$                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 1 ··· (1) 0 1 ··· (2)  REGISTER A+1→ REGISTER A REGISTER Y+1→ REGISTER Y  1 1 1 ··· (3)  REGISTER Y×1→ REGISTER Z | SET REGISTER CALCULATION START DIGIT TO 62 (DECIMAL PORTION 1 DIGIT), AND CALCULATION END DIGIT TO 15 (INTEGER PORTION 1 DIGIT) EXECUTE OPERATION WITH SUBTRACTION OF REGISTER X - REGISTER Z → REGISTER X SET  3 1 2 ··· (4) | 1 2 ··· (5) REGISTER Y+1→ REGISTER Y                                                                                                                                                                  |

| (2) [1](1)<br>1 -[1](3)                                                                                             | (5) [2] [2](4)                                                                                                                                                                                                                |                                                                                                                                                                                                       |

|                                                                                                                     | (1) (1)<br>-(1) (3)                                                                                                                                                                                                           | T(1)  REGISTER A+1→ REGISTER A  T T(3)  REGISTER Y×1→ REGISTER Z  Z(4)  EXECUTE OPERATION WITH SUBTRA  REGISTER X - REGISTER Z  EXECUTE OPERATION WITH SUBTRA  REGISTER X - REGISTER Z → REGIST  T(4) |

| (11) 3.4 3.43(12) R.A. REGISTER Y+0.03 → REGISTER Y  (13) R.Z.                          | SET REGISTER CALCULATION START DIGIT TO 58 (DECIMAL PORTION 4 DIGIT), AND CALCULATION END DIGIT TO 15 (INTEGER PORTION 1 DIGIT) EXECUTE OPERATION WITH SUBTRACTION OF REGISTER X - REGISTER Z → REGISTER X SET  [0.11] [0.1029] [0.0071] (14) | 3.43 3.46 ··· (15)<br>REGISTER Y + 0.03 → REGISTER Y |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| T.73 (11)  REGISTER A+0.03 → REGISTER A  3.43 0.1029 (13)  REGISTER Y×0.03 → REGISTER Z | SET REGISTER CALCULATION (SAND CALCULATION END DIGIT EXECUTE OPERATION WITH SURGISTER Z → FOOTO (0.1029) [0.1029] [1]                                                                                                                         | 3.43 3.46 (18<br>REGISTER Y+0.03 → REGISTER Y        |

| 1.73(11)<br>1.3                                                                         | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                        | (15) 346 71(14)                                      |

| 0 0                                      | TEGISTER A+0.002 → REGISTER A REGISTER Y+0.002 → REGISTER Y                                                                     |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1 (3)                                    |                                                                                                                                 |

| 27 200                                   | SET REGISTER CALCULATION START DIGIT TO 56 (DECIMAL PORTION 6 DIGIT), AND CALCULATION END DIGIT TO 15 (INTEGER PORTION 1 DIGIT) |

| 343 1100                                 | EXECUTE OPERATION WITH SUBTRACTION OF  <br>  REGISTER X - REGISTER Z → REGISTER X SET                                           |

| 3 -1029                                  | 0.007100 0.006924 0.000176(19)                                                                                                  |

| (17) <u>3462</u><br>2 - <u>6924</u> (18) | 3.462(20)                                                                                                                       |

| (20) ··· 3464 176 ··· (19)               | REGISTER Y+0.002 → REGISTER Y                                                                                                   |

|                                          |                                                                                                                                 |

|       | REGISTER X = 3 REGISTER Y = 0 REGISTER W = 0 REGISTER A = 0 | 1](21) | REGISTER A+1→ REGISTER A | ① ···(22)<br>→ REGISTER Z | SET REGISTER CALCULATION START DIGIT TO 62 (DECIMAL PORTION 1 DIGIT), AND CALCULATION END DIGIT TO 15 (INTEGER PORTION 1 DIGIT) | EXECUTE OPERATION WITH SUBTRACTION OF REGISTER X - REGISTER Z → REGISTER X SET | 1 2(23) | 3(24) | → REGISTER B | EGISTER Y |

|-------|-------------------------------------------------------------|--------|--------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------|-------|--------------|-----------|

| - 0.8 | REGISTER X = 3 REC                                          | (1     |                          | 1×1×1→REG                 |                                                                                                                                 | EXECUTE OPERATIO<br>   REGISTER X - REGIS                                      | 3       | 3 (2  |              | → REG     |

FIG. 19

| SET REGISTER CALCULATION START DIGIT TO 59 (DECIMAL PORTION 3 DIGITS), AND CALCULATION END DIGIT TO 15 (INTEGER PORTION 1 DIGIT) | [2.000] [1.200] [0.800] REGISTER X → REGISTER X                                                                  | [0.800] [0.480] [0.320]<br>REGISTER X - REGISTER Z → REGISTER X | $\begin{array}{ccc} \hline 0.320 & \hline 0.064 & \hline 0.256 & \cdots (30) \\ \hline REGISTER X - REGISTER Z \rightarrow REGISTER X \\ \end{array}$ |           |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1<br>REGISTER A+0.4→ REGISTER A<br>3 (1.2 ··· (27)                                                                               | REGISTER W×0.4 $\rightarrow$ REGISTER Z $ \boxed{0.48} \cdots (28) $ REGISTER Y×0.4×0.4 $\rightarrow$ REGISTER Z | $0.064 \cdots (29)$ 0.4 × 0.4 × 0.4 → REGISTER Z                | 11   <u>5.88</u> ··· (31)<br>3×1.4×1.4→ REGISTER B<br>11   11.22)                                                                                     | 1         |

| (26)                                                                                                                             |                                                                                                                  | -1200(27)<br>-480(28)                                           | -64(29)<br>256(30)                                                                                                                                    |           |

|                                                                                                                                  | 300 30                                                                                                           |                                                                 | 300 30                                                                                                                                                | (31) (32) |

|                                                                                                                                           |                                                                          |                                                                      |                                                                                 | <del></del> 7                        |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------|

| SET REGISTER CALCULATION START<br>DIGIT TO 56 (DECIMAL PORTION 6 DIGITS),<br>AND CALCULATION END DIGIT TO 15<br>(INTEGER PORTION 1 DIGIT) | 0.25600 0.235200 0.020800]<br>REGISTER X - REGISTER Z → REGISTER X       | 0.020800] [0.006720] [0.014080] REGISTER X - REGISTER X → REGISTER X | [0.014080] [0.000064] [0.014016]···(37)<br>REGISTER X - REGISTER Z → REGISTER X |                                      |

| REGISTER A+0.04 $\rightarrow$ REGISTER A [5.88] [0.2352](34)                                                                              | REGISTER W $\times$ 0.04 $\rightarrow$ REGISTER Z  [4.2]  [0.00672] (35) | 0.04                                                                 | 3×1.44×1.4                                                                      | 4.32] ··· (39)<br>3×1.44→ REGISTER Y |

| (33)                                                                                                                                      |                                                                          |                                                                      |                                                                                 |                                      |

| 1                                                                                                                                         | - 1200<br>- 1200<br>- 480<br>- 64                                        | 58800 420 256000<br>-235200(34)<br>-6720(35)                         | 64 ··· (36)                                                                     |                                      |

| რ                                                                                                                                         | 120                                                                      | 420                                                                  | 432                                                                             | :: (36)                              |

| (                                                                                                                                         | 2004<br>0044<br>008                                                      | 58800                                                                | 62208                                                                           | :: (38)                              |

-270 240a 260a F REGISTER 16bit SELECTOR **大16bit** [ 16bit 16bit WRITE F/F READ F/F FIG. 21 ADDITION CIRCUIT 16bit 16bit MULTIPLICATION CIRCUIT 260b 16bit **S REGISTER** ADDRESS COUNTER

FIG. 22

| 8 2          |             |         | WRITE AT    |          | X4+Y4×M X5+Y5×M WRITE AT | READ Y5   |          | X5 X5                 | X5 X5 X5               | X2+Y2×M X4+Y4×M X4+Y4×M | PROCESS OF MULTIPLICATION CIRCUIT AND ADDITION CIRCUIT |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|-------------|---------|-------------|----------|--------------------------|-----------|----------|-----------------------|------------------------|-------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2            |             |         | X3+Y3×M W   |          | READ X4, X5 X4           | READ Y4 R |          | X4                    | X3                     | X2+Y2×M X2              | PROCESS AND ADDI                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4            | WRITE AT    |         | X2+Y2×M     | READ Y3  |                          |           | <b> </b> | ХЗ                    | X3                     | M×0++0X                 | STER                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ო            | X1+Y1×M     |         | READ X2, X3 | READ Y2  |                          |           |          | X2                    | X1                     | X0+Y0×M                 | PROCESS OF F REGISTER                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2            | X0+Y0×M     | READ Y1 |             |          |                          |           |          | X                     | X1                     |                         | PROCE                                                  | The second secon |

| <del>-</del> | READ X0, X1 | READ YO |             |          |                          |           |          | 0X                    |                        |                         |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              |             |         |             | <b>_</b> |                          |           |          | OUTPUT OF<br>SELECTOR | CONTENT OF<br>READ F/F | CONTENT OF WRITE F/F    |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

FIG. 24

FIG. 25A FIG. 25C FIG. 25B COMMUNICATION CONTROL SECTION CPU PC **ST31 ST41 ST51** INPUT OPERATION RECEIVE OPERATION DATA TO PC DATA FROM PC NO RESET **ST32** ST42 **CANCELED** SEND OPERATION WRITE OPERATION DATA TO YES DATA IN ST52 **ARITHMETIC UNIT** SHARED MEMORY ∠ST43 **ENABLE BUSY SIGNAL** ST33 **OPERATE CPU ST53** (CANCEL RESET) RECEIVE NO **OPERATION** READ OPERATION **RESULT DATA FROM** ST44 SHARED MEMORY ON **BUSY** YES ∠ST34 SIGNAL? ST54 RECEIVE OPERATION **OPERATION** OFF RESULT ST45 **PROCESS ST35** STOP CPU **ST55 DISPLAY OPERATION** (DURING RESET) WRITE OPERATION **RESULT ST46 RESULT IN** SHARED MEMORY **READ OPERATION END DATA FROM** ST56 SHARED MEMORY **DISABLE BUSY ST47 SIGNAL** SEND OPERATION **RESULT TO PC END**

## FIG. 26

# FIG. 28 **PRIOR ART**

FIG. 29

FIG. 30

FIG. 31A

FIG. 31B

### FIG. 32

**FIG. 33A**

**FIG. 33B**

FIG. 34A

|        |                                      |                        | 40                                      | )11a                   |       |

|--------|--------------------------------------|------------------------|-----------------------------------------|------------------------|-------|

|        | ARBITRARY DIGIT OF                   | PERATION               |                                         |                        |       |

| 4010 ~ | ◆ NUMBER OF<br>OPERATION DIGITS      | 8 [8]                  |                                         | DIG                    | 4013a |

| 4010   | ◆ OPERATION TYPE                     | (1+x)                  | 3-1}                                    | ▼                      |       |

|        | ◆ OPERAND                            | 0.00                   | 123                                     |                        | 4015a |

|        | ♦ OPERATION RESUL                    | тт                     |                                         |                        |       |

|        | ♦ DIGIT INCREASE<br>DISPLAY          |                        | - · · · · · · · · · · · · · · · · · · · |                        |       |

|        | ♦ NUMBER OF<br>UNDERFLOWED<br>DIGITS |                        | ◇ EFFEC<br>PREC                         |                        |       |

|        |                                      | EFFECTIVE<br>PRECISION | DIGIT<br>INCREASE<br>DISPLAY            | DISTINCTIVE<br>DISPLAY |       |

FIG. 34B

|        | ARBITRARY DIGIT OPERATION            |                        |                              |                        |       |  |  |  |

|--------|--------------------------------------|------------------------|------------------------------|------------------------|-------|--|--|--|

| 4010 ~ | ◆ NUMBER OF OPERATION DIGIT          | rs 8                   |                              | DIG                    | ITS   |  |  |  |

|        | ◆ OPERATION TYPE                     | (1+x)                  | <sup>3</sup> -1              | ▼                      |       |  |  |  |

|        | ◆ OPERAND                            | 0.00                   | 123                          |                        |       |  |  |  |

|        | OPERATION RESI                       | ULT 3.694              | 45000 e-3                    |                        | 4017a |  |  |  |

|        | ♦ DIGIT INCREASE<br>DISPLAY          |                        |                              |                        |       |  |  |  |

|        | ♦ NUMBER OF<br>UNDERFLOWED<br>DIGITS |                        | ♦EFFE(<br>PREC               |                        |       |  |  |  |

|        | NUMBER OF<br>UNDERFLOWED<br>DIGITS   | EFFECTIVE<br>PRECISION | DIGIT<br>INCREASE<br>DISPLAY | DISTINCTIVE<br>DISPLAY |       |  |  |  |

# FIG. 35A

|        | ARBITRARY DIGIT OPE          | RATION =           | <u> </u>                     |                       |   |

|--------|------------------------------|--------------------|------------------------------|-----------------------|---|

| 4010 ~ | ◆ NUMBER OF OPERATION DIGITS | 8                  | DIGITS                       |                       |   |

|        | ◆ OPERATION TYPE             | (1+x) <sup>2</sup> | 3-1                          |                       | ▼ |

|        | ◆ OPERAND                    | 0.00               | 123                          |                       |   |

|        | ♦ OPERATION RESULT           | 3.694              | 45000 e-3                    |                       |   |

| 4021a  |                              |                    |                              |                       |   |

|        | NUMBER OF UNDERFLOWED DIGITS | [3]                | ♦EFFE(<br>PREC               |                       |   |

|        |                              | FECTIVE<br>ECISION | DIGIT<br>INCREASE<br>DISPLAY | DISTINCTIN<br>DISPLAY |   |

| ·      | ∤<br>4025a                   |                    |                              |                       | - |

FIG. 35B

FIG. 36A

May 11, 2010

|        | ARBITRARY DIGIT OPERATION            |                                |                        |         |

|--------|--------------------------------------|--------------------------------|------------------------|---------|

| 4010 ~ | ◆ NUMBER OF<br>OPERATION DIGITS      | 8                              | DIGITS                 |         |

|        | ◆ OPERATION TYPE                     | (1+x) <sup>3</sup> -1          | ▼                      |         |

|        | ◆ OPERAND                            | 0.00123                        |                        | i<br>L  |

|        | ♦ OPERATION RESULT                   | 3.6945000 e-3                  |                        |         |

|        | ♦ DIGIT INCREASE<br>DISPLAY          | 3.6945056000 e                 | -3}                    | - 4019a |

|        | ♦ NUMBER OF<br>UNDERFLOWED<br>DIGITS | <b>♦</b> EFFECTIVE             | PRECISION              |         |

| į      |                                      | FECTIVE DIGIT INCREASE DISPLAY | DISTINCTIVE<br>DISPLAY |         |

|        |                                      | )<br>40250                     |                        |         |

FIG. 36B

**FIG. 37A**

FIG. 37B

FIG. 38

# FIG. 39A

|        | ARBITRARY DIGIT OPERATION                                                                 |                        |                              |                        |      |

|--------|-------------------------------------------------------------------------------------------|------------------------|------------------------------|------------------------|------|

| 4000   | ◆ NUMBER OF OPERATION DIGITS                                                              | s 8                    |                              | DIGI                   | тѕ   |

| 4030 ~ | ◆ OPERATION TYPE                                                                          | (1+x) <sup>3</sup>     | 3-1                          | ▼                      |      |

|        | ◆ OPERAND                                                                                 | 0.001                  | 123                          |                        |      |

|        | <ul><li>◇ OPERATION RESULT</li><li>◇ DIGIT INCREASE DISPLAY</li><li>◇ NUMBER OF</li></ul> | LT                     | ♦ EFFE                       |                        | 4031 |

|        | UNDERFLOWED<br>DIGITS                                                                     |                        | PREC                         |                        |      |

| :      |                                                                                           | EFFECTIVE<br>PRECISION | DIGIT<br>INCREASE<br>DISPLAY | DISTINCTIVE<br>DISPLAY |      |

FIG. 39B

|        | ARBITRARY DIGIT O                    | PERATION ■             |                              |                        |            |         |

|--------|--------------------------------------|------------------------|------------------------------|------------------------|------------|---------|

| 4030 ~ | ◆ NUMBER OF OPERATION DIGITS         | 8                      |                              |                        | DIGITS     |         |

|        | ◆ OPERATION TYPE                     | (1+x)                  | 3-1                          |                        | <b>-</b> ] |         |

|        | ◆ OPERAND                            | 0.00                   | 123                          |                        |            |         |

|        | OPERATION RESUL                      | T 3.694                | 45406 e-3                    | }                      |            | - 4031a |

|        | ♦ DIGIT INCREASE<br>DISPLAY          |                        |                              |                        |            |         |

|        | ♦ NUMBER OF<br>UNDERFLOWED<br>DIGITS |                        | ♦EFFE(<br>PREC               |                        |            |         |

|        |                                      | EFFECTIVE<br>PRECISION | DIGIT<br>INCREASE<br>DISPLAY | DISTINCTIVE<br>DISPLAY |            |         |

DECIMAL COMPUTING APPARATUS, ELECTRONIC DEVICE CONNECTABLE DECIMAL COMPUTING APPARATUS, ARITHMETIC OPERATION APPARATUS, ARITHMETIC OPERATION CONTROL APPARATUS, AND PROGRAM-RECORDED RECORDING MEDIUM

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to an arithmetic unit, such as a decimal calculation apparatus.

#### 2. Description of the Related Art

Arithmetic systems equipped with an arithmetic unit, such 15 as a CPU (Central Processing Unit), are popular. There are various standards for an arithmetic unit, a memory and so forth which constitute an arithmetic system. The ANSI/IEEE 754-1985 standard (hereinafter simply called "IEEE 754") is an operation standard defining, for example, a binary floating-point operation. The IEEE 754 defines the numerical form (precision) that is handled in a binary floating-point operation in three types, namely, single precision (32 bits), double precision (64 bits) and long double precision (96 bits).

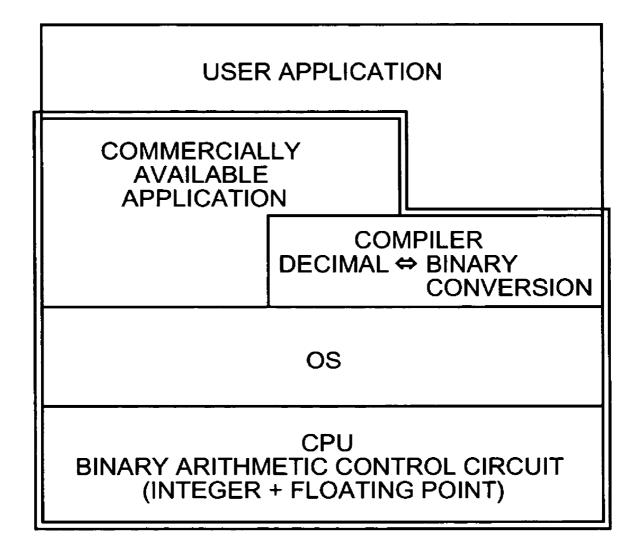

FIG. **28** is a diagram showing one example of the logical <sup>25</sup> hierarchical structure of a conventional arithmetic system. The arithmetic system has a hierarchical structure having a CPU or an arithmetic unit as the lowermost layer, and an OS (Operating System) or the basic software which controls the CPU, a compiler which converts an overlying application <sup>30</sup> program written in a high-level language to a machine-language program, a commercially available application, such as spreadsheet software or wordprocessing software, and a user application layered in order over the bottom layer.

As the conventional arithmetic system is built up as a <sup>35</sup> circuit which performs an operation with a given precision (number of effective digits) as defined in, for example, the IEEE 754, it has the following shortcomings.

# (1) Restriction on the Number of Effective Digits

The operation precision or the number of effective digits in the arithmetic system comprising the conventional arithmetic unit is limited to precisions defined by the operation standard (three types in the IEEE 754). That is, an operation with other numbers of digits than the specified number of effective digits cannot be performed. This disables execution of an operation with the exact precision required.

### (2) Error in Binary Operation

As the arithmetic unit performs a binary operation, numerical data in the arithmetic system is expressed in binary notation. This requires binary-decimal conversion, so that an conversion-originated error is inevitable. In convergent calculation or the like, for example, every time a repetitive operation is performed, the error becomes larger with the restriction on the number of effective digits. To cancel the error, binary operations should be performed with a precision higher than the precision of decimal operations.

# (3) Complex Program Writing Due to Restriction on the Number of Effective Digits

The arithmetic unit is constructed in such a way as to perform an operation with a precision defined by the operation standard. Therefore, a machine instruction code is written in such a way as to perform an operation with an operation precision (number of effective digits) of the arithmetic unit, 65 and the precision (number of effective digits) of an instruction code is fixed. As the precision (number of effective digits)

2

cannot be designated in an instruction code itself, the precision should be coped with by a program, thus making program writing complex.

#### SUMMARY OF THE INVENTION

Accordingly, it is an object of the invention to provide a decimal calculation apparatus which can freely set the number of calculation digits at the time of performing calculation with a calculation instruction, and efficiently executes calculation in the set number of calculation digits with small-size calculation means

To achieve the object, according to one aspect of the invention, there is provided a decimal calculation apparatus which performs multidigit decimal calculation with a number of calculation digits set in a calculation instruction, and comprises:

a multidigit memory section (e.g., a register section **360** in FIG. **9**) capable of storing values with greater numbers of digits than a number of digits of a predetermined digit unit in a plurality of memory areas;

a calculation-instruction memory section (e.g., a program ROM **310** in FIG. **9**) which stores a calculation instruction having a number of calculation digits and a type of calculation set therein; and

a decimal calculation section (e.g., a computing unit 370 in FIG. 9) which performs decimal calculation of sequentially calculating numerical values of corresponding digit units respectively stored in the plurality of memory areas of the multidigit memory section, the digit unit by the digit unit in the number of calculation digits set in the calculation instruction stored in the calculation-instruction memory section, in decimal calculation according to the type of calculation set in the calculation instruction stored in the calculation-instruction memory section, and sequentially writing calculation results in the plurality of memory areas of the multidigit memory section the digit unit by the digit unit.

#### BRIEF DESCRIPTION OF THE DRAWINGS

These objects and other objects and advantages of the present invention will become more apparent upon reading of the following detailed description and the accompanying drawings in which:

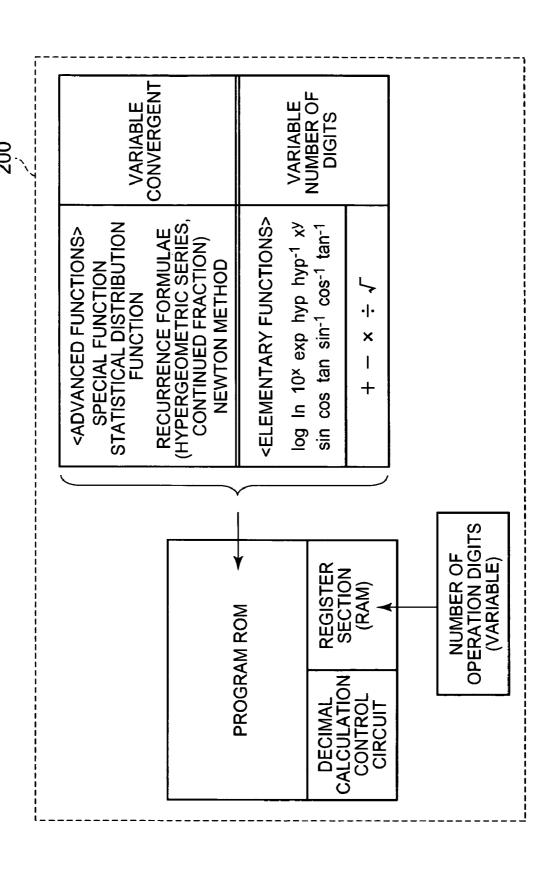

FIG. 1 is a schematic diagram showing the fundamental structure of an arithmetic unit embodying the invention;

FIG. 2A is a schematic structural diagram of an arithmetic system according to a first embodiment of the invention;

FIG. 2B is a schematic structural diagram of the arithmetic system according to the first embodiment

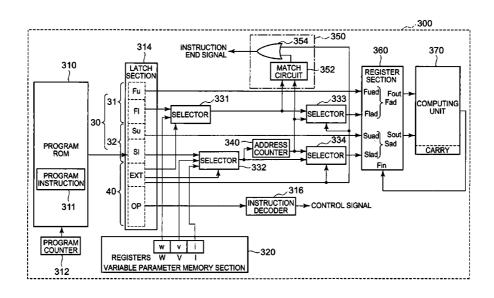

FIG. 3 is a circuit structural diagram of the essential portions of an arithmetic unit according to the first embodiment;

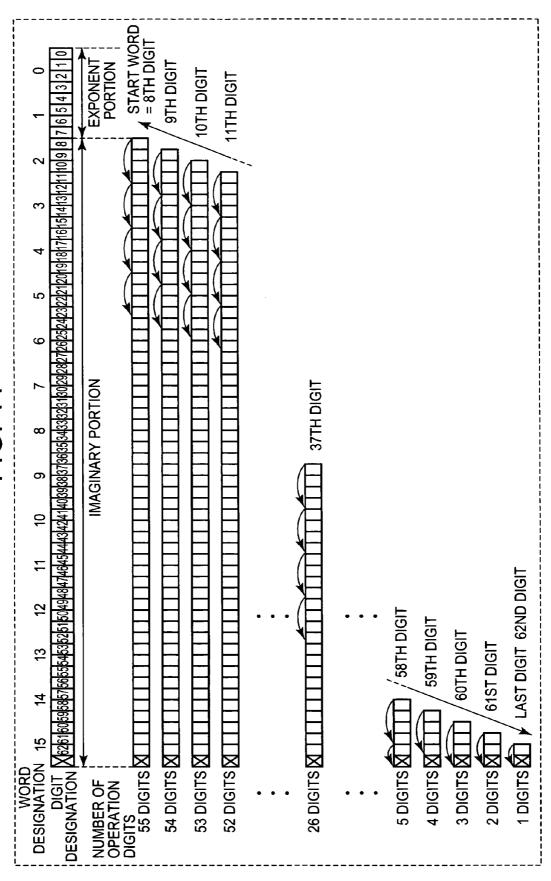

FIG. 4 is a structural diagram of a register section;

FIG. 5 shows the correlation between upper addresses Fuad and Suad, and a designated register;

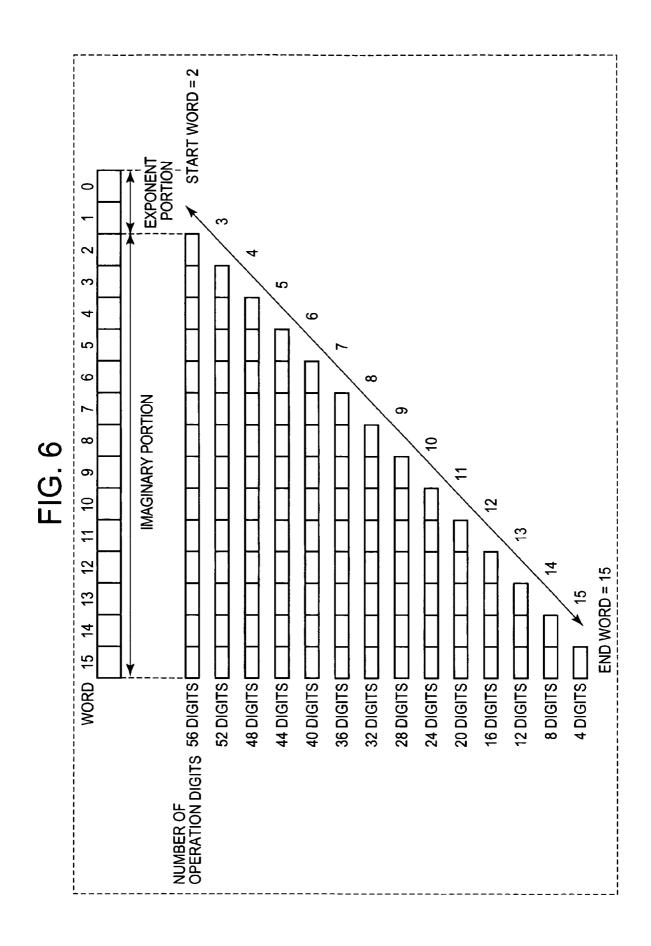

FIG. 6 is a diagram showing a change in the number of operation digits caused by a change in a start word according to the first embodiment;

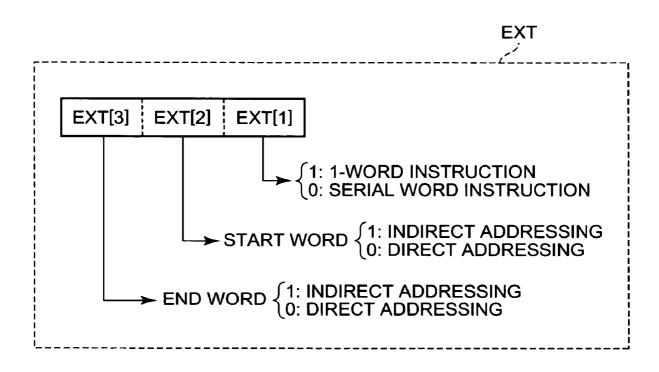

FIG. 7 shows the structure of an extended instruction code  $_{60}\,$  EXT according to the first embodiment;

FIG. 8 shows the correlation between an extended instruction code EXT and an functional example of the arithmetic unit according to the first embodiment;

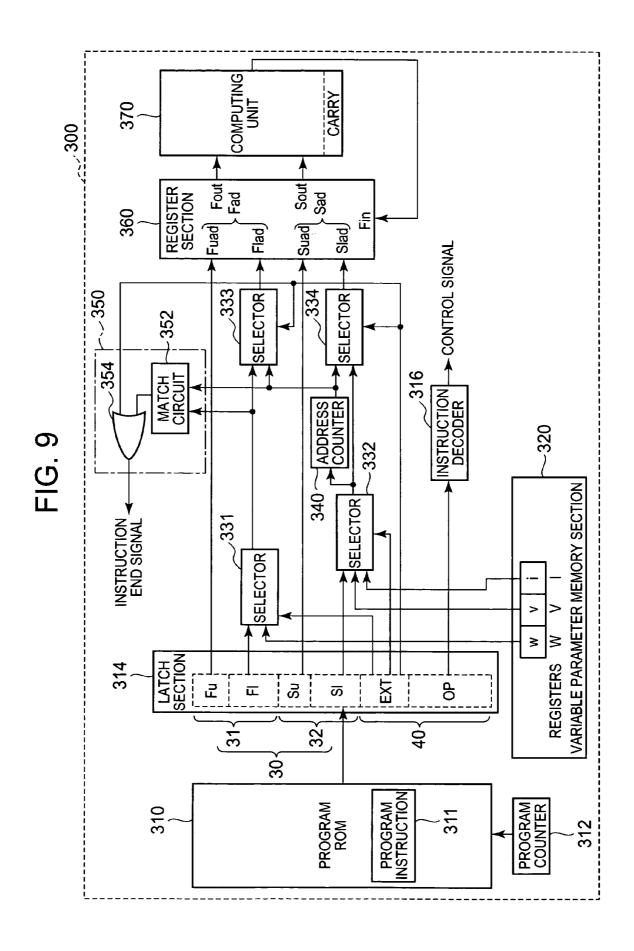

FIG. 9 is a circuit structural diagram of the essential portions of an arithmetic unit according to a second embodiment;

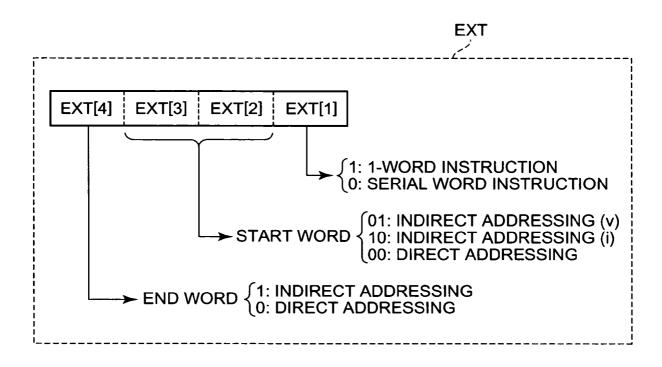

FIG. 10 shows the structure of an extended instruction code EXT according to the second embodiment;

- FIG. 11 is a diagram showing a change in the number of calculation digits caused by a change in a calculation start digit according to the second embodiment;

- FIG. 12 shows the correlation between an extended instruction code EXT and an functional example of the arithmetic unit according to the second embodiment;

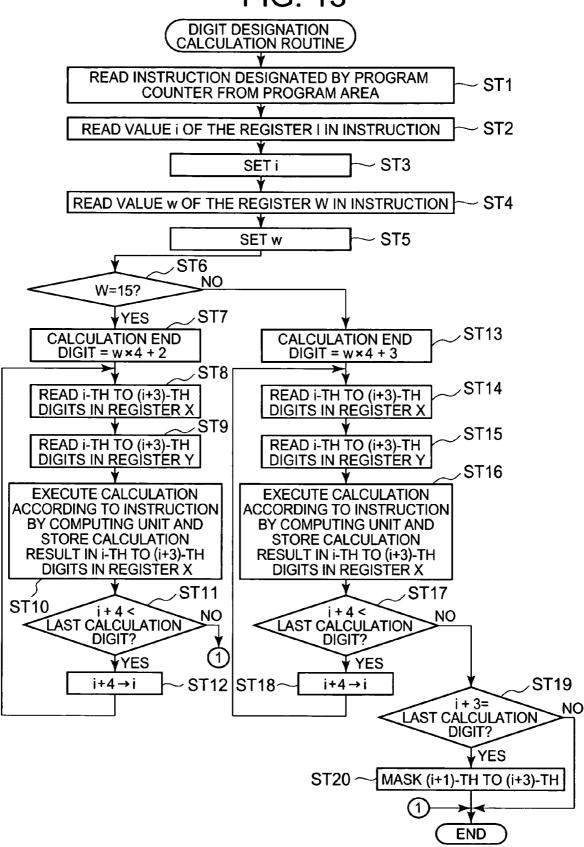

- FIG. 13 is a flowchart illustrating a digit designation calculation routine:

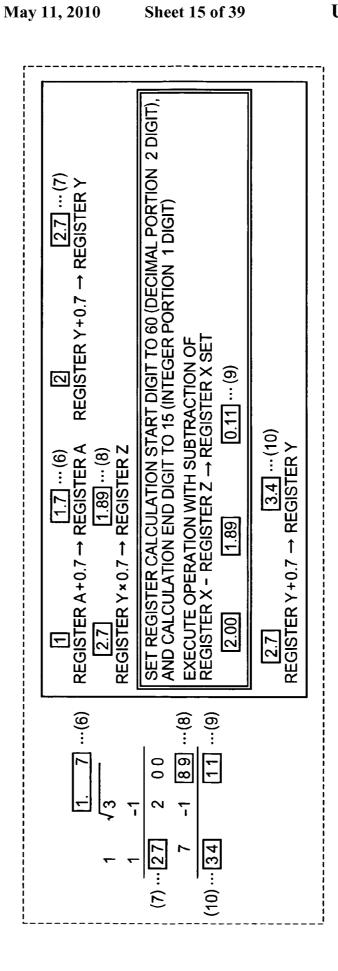

- FIG. **14** is a diagram illustrating a square root operation routine in the arithmetic unit according to the second embodiment:

- FIG. 15 is a diagram illustrating the square root operation routine in the arithmetic unit according to the second embodiment:

- FIG. **16** is a diagram illustrating the square root operation 15 routine in the arithmetic unit according to the second embodiment:

- FIG. 17 is a diagram illustrating the square root operation routine in the arithmetic unit according to the second embodiment:

- FIG. **18** is a diagram illustrating a cube root operation routine in the arithmetic unit according to the second embodiment;

- FIG. **19** is a diagram illustrating the cube root operation routine in the arithmetic unit according to the second embodi- 25 ment;

- FIG. 20 is a diagram illustrating the cube root operation routine in the arithmetic unit according to the second embodiment;

- FIG. 21 is a block diagram of the components of a third 30 embodiment;

- FIG. 22 is a diagram illustrating a timing chart;

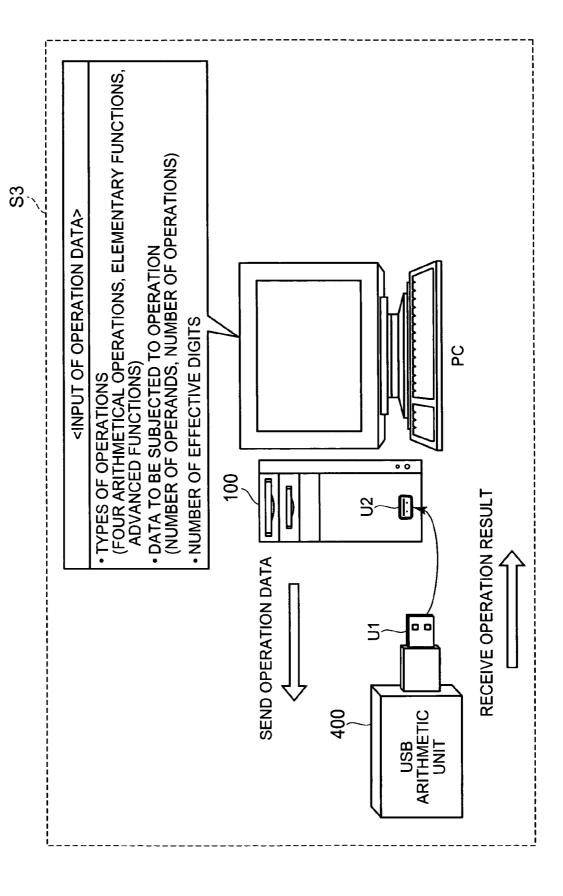

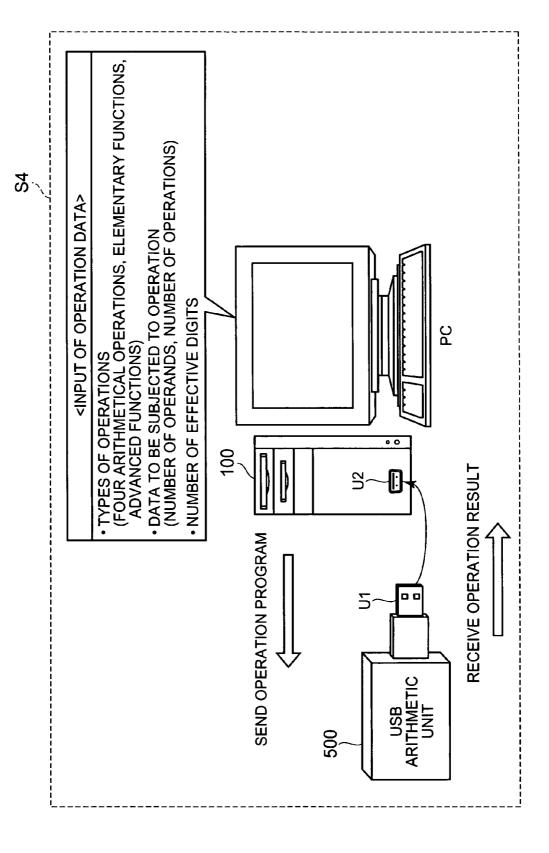

- FIG. 23 is a schematic structural diagram of an arithmetic system according to a fourth embodiment;

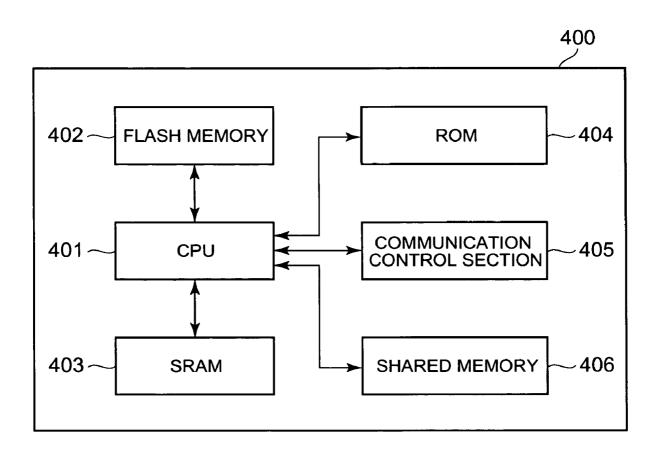

- FIG. 24 is a block diagram showing the structures of the 35 essential portions of a USB arithmetic unit;

- FIG. 25A is a flowchart illustrating a communication routine which is executed by a personal computer;

- FIG. **25**B is a flowchart illustrating a communication routine which is executed by a communication control section;

- FIG. **25**C is a flowchart illustrating a communication routine which is executed by a CPU;

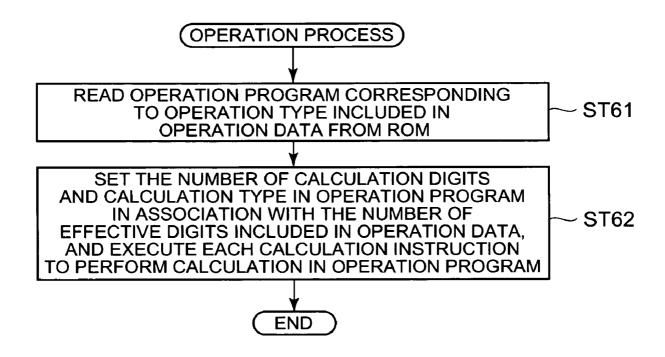

- FIG. **26** is a flowchart illustrating an operation process which is executed by the CPU;

- FIG. 27 shows a modification of the fourth embodiment; 45

- FIG. 28 is a diagram showing the logical hierarchical structure of a conventional arithmetic system;

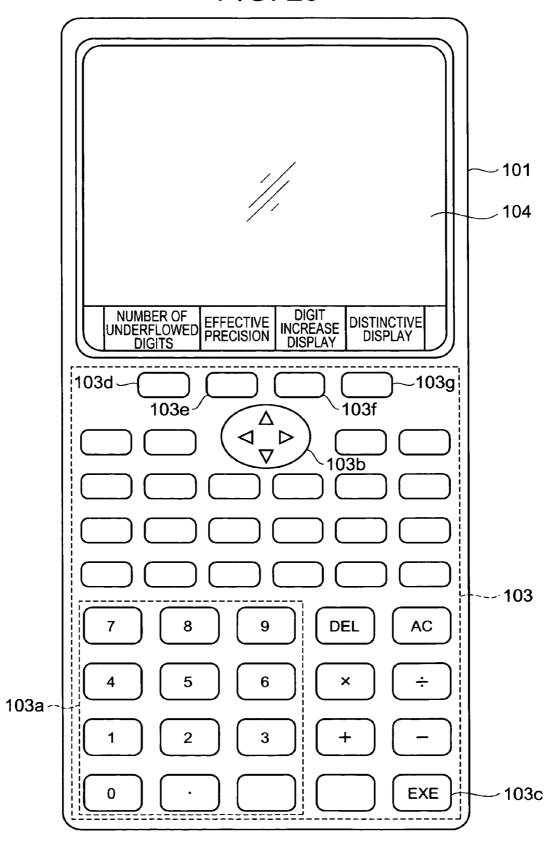

- FIG. **29** is a schematic diagram of a graph function electronic calculator to which the invention is adapted;

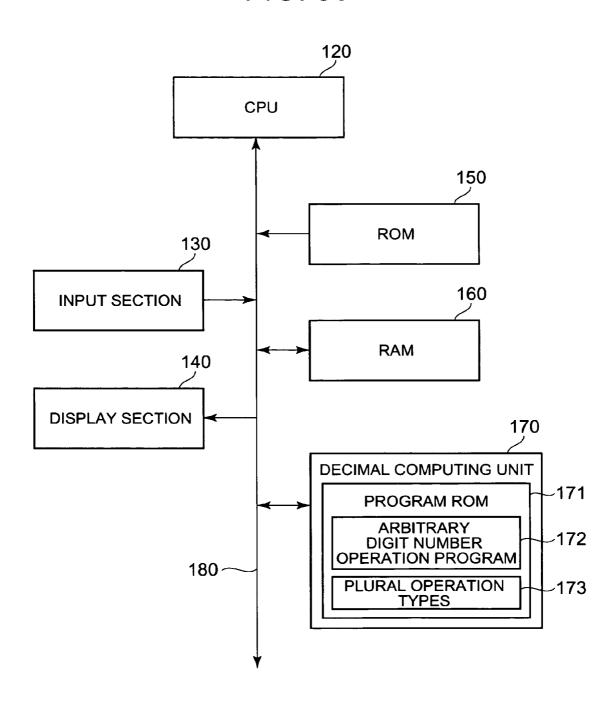

- FIG. **30** is a block diagram showing the internal structure of 50 the graph function electronic calculator to which the invention is adapted;

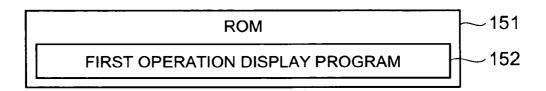

- FIG. 31A is a diagram showing the data structure of a ROM according to a fifth embodiment;

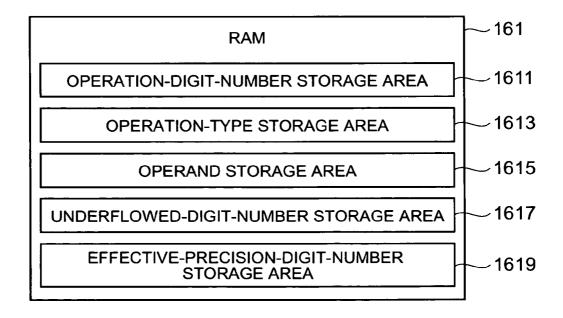

- FIG. **31**B is a diagram showing the data structure of a RAM 55 according to the fifth embodiment;

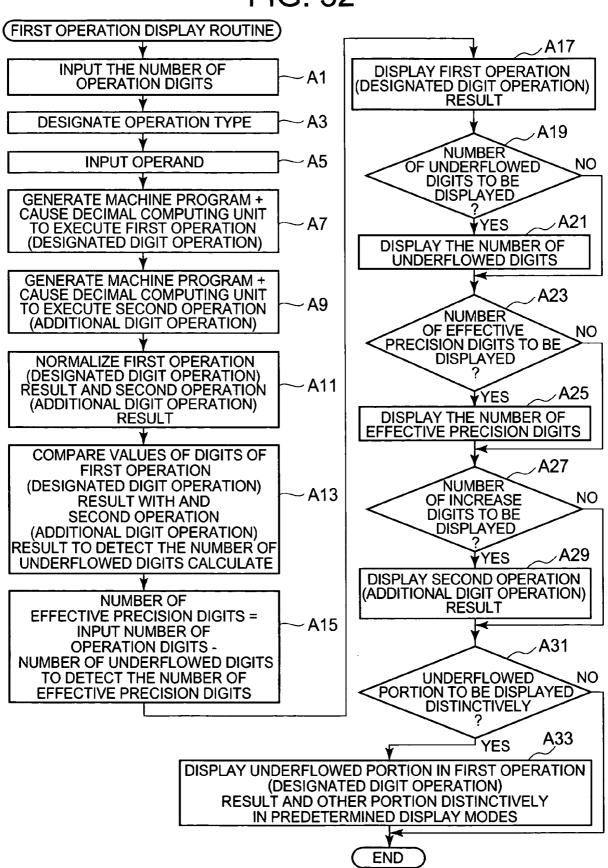

- FIG. 32 is a flowchart illustrating the flow of a first operation (designated digit operation) display routine;

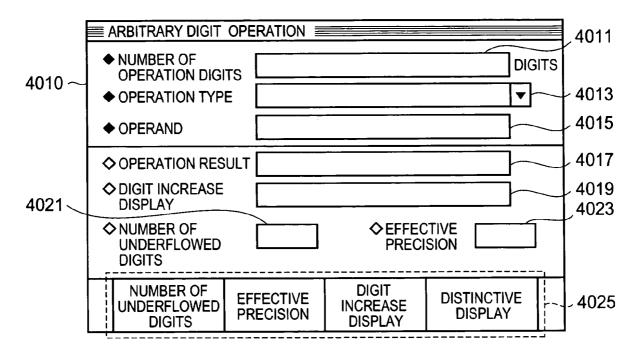

- FIG. **33**A is a diagram showing one example of a display screen to be displayed in the first operation (designated digit 60 operation) display routine;

- FIG. **33**B is a diagram showing one example of a display screen when an operation type is designated;

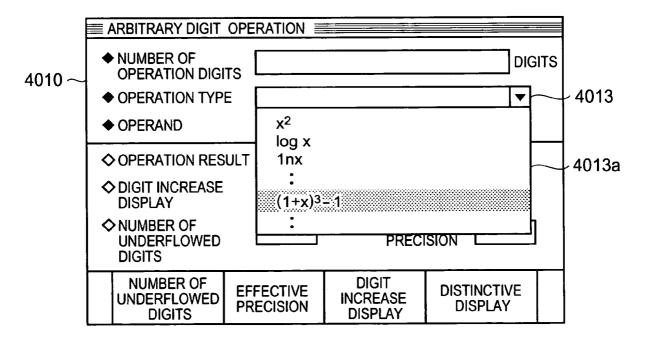

- FIG. **34**A is a diagram showing one example of a display screen when entry of the number of operation digits, designation of an operation type and entry of an operand are carried out:

4

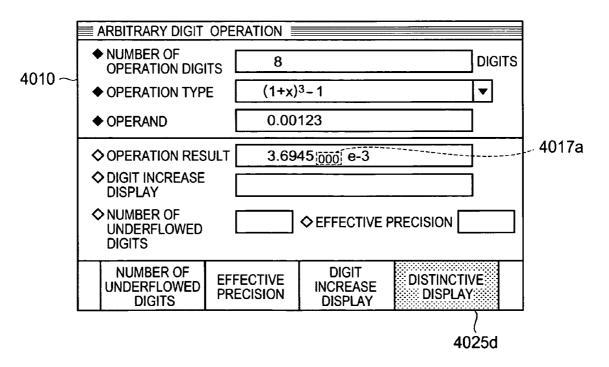

- FIG. **34**B is a diagram showing one example of a display screen when the result of the first operation (designated digit operation) is displayed;

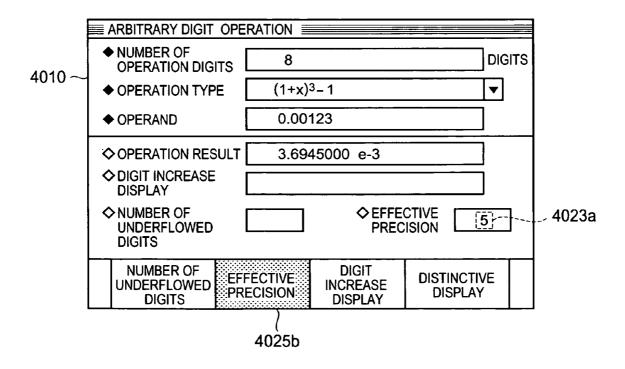

- FIG. **35**A is a diagram showing one example of a display screen when an underflow digit number display instruction is given;

- FIG. **35**B is a diagram showing one example of a display screen when an effective precision digit number display instruction is given;

- FIG. **36**A is a diagram showing-one example of a display screen when a digit number increase display instruction is given:

- FIG. **36**B is a diagram showing one example of a display screen when an underflow portion identification instruction is given:

- FIG. 37A is a diagram showing the data structure of a ROM according to a sixth embodiment;

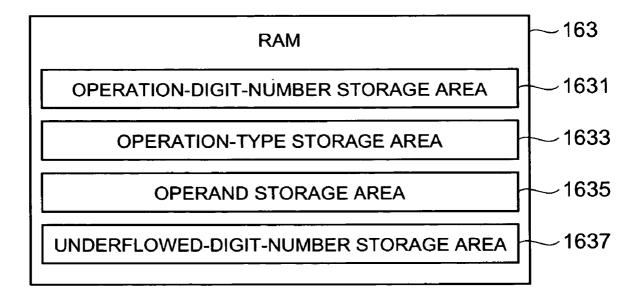

- FIG. 37B is a diagram showing the data structure of a RAM according to the sixth embodiment;

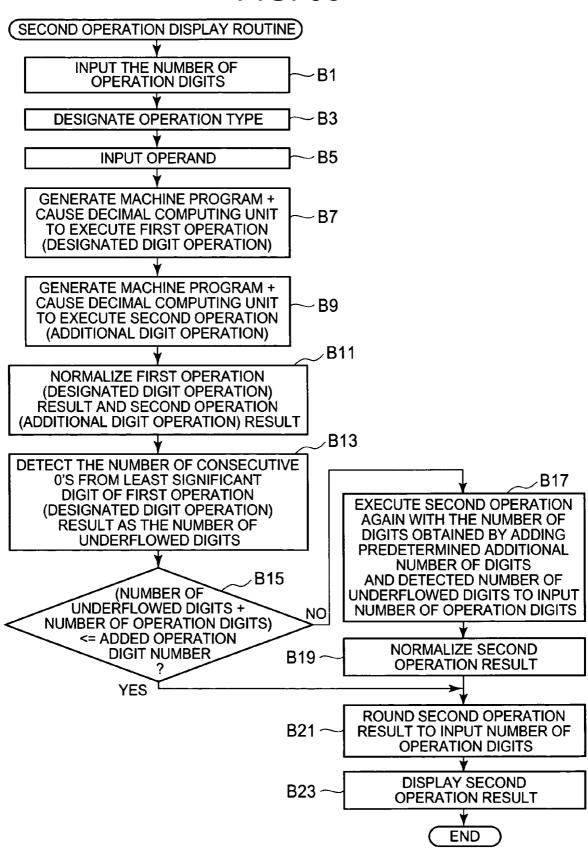

- FIG. 38 is a flowchart illustrating the flow of a second operation (additional digit operation) display routine;

- FIG. **39**A is a flowchart showing one example of a display screen when entry of the number of operation digits, designation of an operation type and entry of an operand are carried out in the second operation (additional digit operation) display routine; and

- FIG. **39**B is a flowchart showing one example of a display screen when the underflowed result of the second operation (additional digit operation) is displayed.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

#### First Embodiment

A first embodiment to carry out the invention will be described below with reference to the accompanying drawings.

FIG. 1 is a schematic diagram showing the fundamental structure of an arithmetic unit 200 according to the first embodiment. The arithmetic unit 200 comprises a program ROM which stores an operation program, an arithmetic control circuit which reads the operation program and runs it, and a register section for temporarily storing operation data.

The number of operation digits (number of effective digits) of the register section is variable to achieve a variable number of operation digits in arithmetical operations of addition, subtraction, multiplication and division, basic operations on a square root or the like, and operations of elementary functions, such as a logarithmic function and a trigonometric function, and also achieve variable convergent conditions in operations of advanced functions, such as special functions and statistical distribution functions, and operations on recurrence formulae or the like. The arithmetic control circuit also performs decimal operations to prevent occurrence of an error originating from binary-to-decimal conversion.

A specific example of an arithmetic system equipped with such an arithmetic unit.

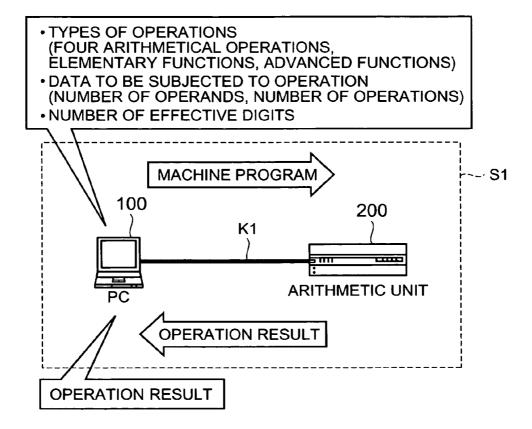

FIG. 2A is a schematic structural diagram of an arithmetic system S1. The arithmetic system S1 comprises a PC (Personal Computer) 100 and an arithmetic unit 200. The PC 100 and the arithmetic unit 200 are connected together by a communication cable K1 like a USB (Universal Serial Bus) cable so as to be able to exchange data with each other.

The PC 100 is achieved by a computer which comprises a CPU (Central Processing Unit), ROM (Read Only Memory), RAM (Random Access Memory), an input device, such as a

keyboard and a mouse or the like, a display device, and a communication unit having a connection terminal to which the communication cable K1 is connectable. The PC 100 serves as a man-machine interface between the arithmetic system S1 and a user.

The PC 100 generates a machine program based on the number of operation arbitrarily designated by a user, the types of operations (arithmetical operations, elementary functions, advanced functions, etc.) and initial data values to be subjected to operations, and transfers the machine program to the arithmetic unit 200, which perform the operations. The results of the operations done by the arithmetic unit 200 are displayed on the display device.

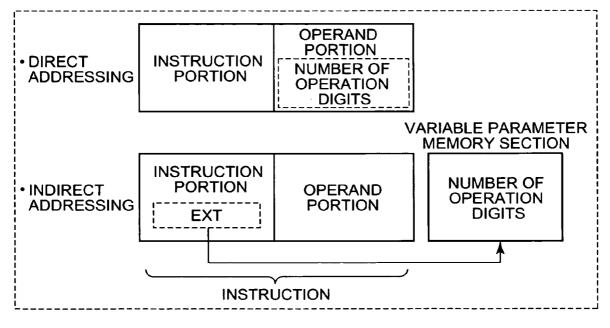

The arithmetic unit **200** executes numerical operations according to the machine program transferred from the PC **15 100**, and, particularly, performs an operation on each of instructions constituting the machine program in the number of operation digits that is designated in that instruction. The arithmetic unit **200** sends the operation result to the PC **100**. The numerical operations which are executed by the arithmetic unit **200** are classified into two, (1) a direct addressing type and (2) an indirect addressing type, according to how the number of operation digits is designated.

As shown in FIG. 2B, the direct addressing type is an instruction type to directly designate the number of operation 25 digits in an operand portion. The arithmetic unit 200 executes a numerical operation on an instruction in the number of operation digits designated in the operand portion of the instruction

The indirect addressing type is an instruction type to designate the location where the number of operation digits is stored (i.e., to indirectly designate the number of operation digits). The arithmetic unit **200** reads the number of operation digits from a location designated by an instruction, and executes a numerical operation on the instruction in the read 35 number of operation digits.

FIG. 3 is a block diagram showing the circuit structure of the arithmetic unit 200, and shows the essential portions that are associated with execution of numerical operations. Referring to FIG. 3, the arithmetic unit 200 comprises a program 40 ROM 210, a program counter 212, a latch section 214, an instruction decoder 216, a variable parameter memory section 220, selectors 231, 232, 233 and 234, an address counter 240, a register section 260, a computing unit 270, and an end decision circuit 250.

The program ROM 210, which is constructed by, for example, an EEPROM (Electrical Erasable Programmable ROM) that is an electrically programmable memory, stores a machine program transferred from the PC 100 as a program instruction 211. The program instruction 211 is comprised of one or more calculation instructions in each of which the type of calculation and the number of calculation digits are set. Program instructions 211 stored in the program ROM 210 at addresses indicated by the address counter 240 are read out one after another and are stored in the latch section 214. The program ROM 210 may be replaced with an electrically programmable non-volatile RAM or the like. The latch section 214, which is constituted by a programmable memory, such as RAM, holds a single instruction read from the program ROM 210.

A single instruction comprises an instruction portion  ${\bf 10}$  and an operand portion  ${\bf 20}$ .

The instruction portion 10 has an instruction code OP and a 3-bit extended instruction code EXT. The operand portion 20 has a first operand portion 21 and a second operand portion 65 22 each consisting of six bits. The first operand portion 21 comprises 2-bit data Fu and 4-bit data F1, and the second

operand portion **22** comprises 2-bit data Su and 4-bit data S1. The details of those data will be given later.

The instruction decoder 216 decodes the instruction code OP latched in the latch section 214, and outputs various control signals for execution of various control circuits in the arithmetic unit 200. For example, the instruction decoder 216 sends the computing unit 270 an operation control signal for allowing the computing unit 270 to execute the decoded instruction.

The variable parameter memory section **220**, constituted by a RAM or the like, has registers W and V each capable of storing 4-bit data. In case of indirect addressing, the number of operation digits is stored in the registers W and V which store values to be the number of operation digits in a changeable manner.

The selector **231** receives the data F1 latched in the latch section **214** and data stored in the register W (hereinafter called "data w"), and receives data of the third bit in the extended instruction code EXT (hereinafter called "data EXT [3]) as a select control signal. The selector **231** selects and outputs one of the two input data according to the select control signal or the value of the data EXT[3]. Specifically, the selector **231** selectively outputs the data when the value of the data EXT[3] is "1", and selectively outputs the data F1 when the value of the data EXT[3] is "0".

The selector 232 receives the data S1 latched in the latch section 214 and data stored in the register V (hereinafter called "data v"), and receives data of the second bit in the extended instruction code EXT (hereinafter called "data EXT [2]) as a select control signal. The selector 232 selects and outputs one of the two input data according to the select control signal or the value of the data EXT[3]. Specifically, the selector 232 selectively outputs the data v when the value of the data EXT[2] is "1", and selectively outputs the data S1 when the value of the data EXT[2] is "0".

The address counter **240** is a 4-bit up counter in which the output data of the selector **232** is set as an initial value. The address counter **240** counts up in synchronism with an internal clock, and outputs a present count value.

The selector 233 receives the output data of the selector 231 and the output data of the address counter 240 (count value), and receives data of the first bit in the extended instruction code EXT (hereinafter called "data EXT[1]) as a select control signal. The selector 233 selects and outputs one of the two input data according to the value of the data EXT[1]. Specifically, the selector 233 selectively outputs the output data of the selector 231 when the value of the data EXT[1] is "1", and selectively outputs the output data of the address counter 240 when the value of the data EXT[2] is "0".

The selector 234 receives the output data of the selector 232 and the output data of the address counter 240, and receives the data EXT[1] as a select control signal. The selector 234 selects and outputs one of the two input data according to the value of the data EXT[1]. Specifically, the selector 234 selectively outputs the output data of the selector 232 when the value of the data EXT[1] is "1", and selectively outputs the output data of the address counter 240 when the value of the data EXT[2] is "0".

The end decision circuit **250** has a match circuit **252** and an 60 OR gate **254**.

The match circuit 252 receives output data of the selector 231 and output data of the address counter 240, and outputs a match signal "1" when both input data match with each other, and outputs an unmatch signal "0" when they do not match with each other. The output signal of the match circuit 252 and data EXT[1] are input to the OR gate 254, which in turn outputs a signal of the logic sum of the two input signals.

6

Therefore, the end decision circuit 250 outputs an instruction end signal "1" when the output data of the address counter 240 matches with the output data of the selector 231 or when the value of the data EXT[1] is "1", and outputs an instruction continue signal "0" otherwise.

7

The register section 260, constituted by a RAM or the like, is a data register which stores values of the individual digits of BCD coded operation data in the order of addresses every predetermined number of digits. The register section 260 is a nation and data output.

At the first port, 16-bit data stored at a 6-bit address Fad with 2-bit data input from an address terminal Fuad as an upper address and 4-bit data input from an address terminal Flad as a lower address is output from an output terminal Fout. Data Fu latched in the latch section 214 is input to an address terminal Fuad, and output data of the selector 233 is input to an address terminal Flad.

At the second port, 16-bit data stored at a 6-bit address Sad with 2-bit data input from an address terminal Suad as an upper address and 4-bit data input from an address terminal Slad as a lower address is output from an output terminal Sout. Data Su latched in the latch section 214 is input to an address terminal Suad, and output data of the selector 234 is input to an address terminal Slad.

16-bit data is input to the register section 260 from an input terminal Fin, and is written at the address ad.

The computing unit 270 capable of performing a 16-bit operation performs an operation according to an operation control signal input from the instruction decoder 216 the invention while the instruction end signal "1" is not output from the end decision circuit 250 (i.e., while the instruction continue signal "0" is output). In other words, the computing unit 270 receives 16-bit data output from each of the output terminals Fout and Sout of the register section 260, performs an operation on the two input data, and outputs the operation result as 16-bit data. The output data (operation result) of the computing unit 270 is input to the input terminal Fin of the register section 260 and written in the register section 260.

FIG. 4 is a diagram showing the detailed structure of the register section 260. Referring to the diagram, the register section 260 has four registers X, Y, Z and A each has a capacity of 16 words. One word consists of 16 bits and operation data is stored in a BCD coded form, so that one word is equivalent to four digits in decimal notation. Each register stores data of a floating-point type whose format has upper 14 words (second to fifteenth words) as an imaginary portion and lower two words (0-th word to the first word) as an exponent portion (including a sign).

The register section 260 is addressed by designating a register with a 2-bit upper address and designating a word in the register with a 4-bit lower address. That is, addressing of the register section 260 is executed word by word, and one word of data or 16-bit data is output. The values of the upper  $_{55}$ addresses Fuad and Suad are associated with the registers as shown in a data table in FIG. 5. The value of each of the lower addresses Flad and Slad indicates a word.